Project no: 100204

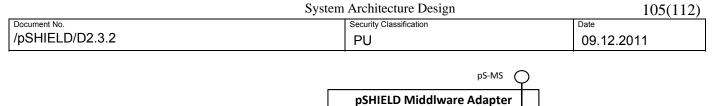

### pSHIELD

pilot embedded Systems arcHItecturE for multi-Layer Dependable solutions

Instrument type: Capability Project

Priority name: Embedded Systems / Rail Transportation Scenarios

# **System Architecture Design**

# For the pSHIELD-project

### Deliverable D2.3.2

### Partners contributed to the work:

HAI, Greece SE, Italy UNIROMA1, Italy ATHENA, Greece, THYIA, Slovenia ETH, Italy SESM, Italy, CS, Portugal, CWIN, Norway

| Project co-funded by the European Commission within the Seventh Framework Programme (2007-2012) |                                                                                       |   |  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|--|

| Dissemination Level                                                                             |                                                                                       |   |  |

| PU                                                                                              | Public                                                                                | Х |  |

| PP                                                                                              | Restricted to other programme participants (including the Commission Services)        |   |  |

| RE                                                                                              | Restricted to a group specified by the consortium (including the Commission Services) |   |  |

| CO                                                                                              | Confidential, only for members of the consortium (including the Commission Services)  |   |  |

| Autho                 | s and App |      |           |

|-----------------------|-----------|------|-----------|

| Name                  | Company   | Date | Signature |

| Nikos Pappas          | HAI       |      |           |

| Andrea Morgagni       | SE        |      |           |

| Vincenzo Suraci       | UNIROMA1  |      |           |

| Kyriakos Stefanidis   | ATHENA    |      |           |

| Athanasios Poulakidas | HAI       |      |           |

| Ljiljana Mijić        | THYIA     |      |           |

| Spase Drakul          | THYIA     |      |           |

| Nastja Kuzmin         | THYIA     |      |           |

| Paolo Azzoni          | ETH       |      |           |

| Emilio Bisbiglio      | SESM      |      |           |

| João Cunha            | SESM      |      |           |

| Przemyslaw Osocha     | SESM      |      |           |

| Baldelli Renato       | SE        |      |           |

| Andrea Fiaschetti     | UNIROMA1  |      |           |

| Jose Verissimo        | CS        |      |           |

| Mohammad Chowdhury    | CWIN      |      |           |

| Reviewe               | d by      |      |           |

| Name                  | Company   |      |           |

|                       |           |      |           |

| Approve               | d by      |      |           |

| Name                  | Company   |      |           |

Pilot SHIELD

pilot embedded Systems arcHltecturE for multi-Layer Dependable solutions

| Modification History |            |                                          |  |

|----------------------|------------|------------------------------------------|--|

| Issue                | Date       | Description                              |  |

| Draft A              | 26.10.2011 | Issue for comments, connection to D2.3.1 |  |

| Issue 1              | 22.11.2011 | SPD Requirements, Interfaces             |  |

| Issue 2              | 24.11.2011 | Overlay additions                        |  |

| Issue 3              | 01.12.2011 | Network Interfaces and Review            |  |

| Issue 4              | 09.12.2011 | Final                                    |  |

| Issue 5              |            |                                          |  |

| Issue 6              |            |                                          |  |

| Issue 7              |            |                                          |  |

# Contents

| Exec  | utive Sur                          | nmary                                                                                                | 11       |

|-------|------------------------------------|------------------------------------------------------------------------------------------------------|----------|

| Intro | duction                            |                                                                                                      | 12       |

| Term  | ns, Definit                        | ions and Approaches                                                                                  | 13       |

| 3.1   | Cross-La                           | yer / Cross-Overlay Architecture Definitions                                                         | 15       |

|       | 3.1.1<br>3.1.2<br>3.1.2.1          | Introduction<br>Description of Cross-Layer Architecture<br>A definition for Cross-Layer Design (CLD) | 15<br>16 |

|       | 3.1.2.1                            | A definition for Closs-Layer Design (CLD)                                                            |          |

|       | 3.1.2.2                            | Existing and new CLAs                                                                                |          |

|       | 3.1.2.3                            | Challenges                                                                                           |          |

|       | 3.1.2.4                            | Description of Layers                                                                                |          |

|       | 3.1.3                              | The Overlay as a Cross-Layer Security Architecture for Security, Privacy and Dependability           |          |

|       | 3.1.3.1                            | Security                                                                                             |          |

|       | 3.1.3.2                            | Dependability                                                                                        | 24       |

| 3.2   | Node Lay                           | yer Definitions                                                                                      | 24       |

|       | 3.2.1<br>3.2.1.1                   | Nano and Micro/Personal Node<br>Technology Description                                               |          |

|       | 3.2.2<br>3.2.3<br>3.2.3.1          | Power Node<br>Cryptography Technologies<br>Attacks on Cryptosystems                                  | 26<br>28 |

|       | 3.2.3.2                            | Attacks on Protocols                                                                                 | 28       |

|       | 3.2.3.3                            | Asymmetric Cryptography                                                                              | 29       |

|       | 3.2.3.4                            | Symmetric Cryptography                                                                               |          |

|       | 3.2.3.5                            | Message Authentication Codes                                                                         |          |

|       | 3.2.3.6                            | Key Management                                                                                       |          |

| 3.3   | Network                            | Layer Definitions                                                                                    | 30       |

|       | 3.3.1<br>3.3.2<br>3.3.3            | General Network Layer description<br>Software Defined Radio<br>Cognitive Radio                       | 30<br>31 |

| 3.4   | Middlewa                           | are Layer Definitions                                                                                | 33       |

|       | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.3.1 | SPD Driven Semantics<br>Core SPD Services<br>Policy-based Management<br>Policy Management Tool       | 35<br>37 |

|       | 3.4.3.2                            | Policy Decision Point                                                                                | 38       |

|       | 3.4.3.3                            | Policy Enforcement Point                                                                             | 38       |

| 3.5   | Overlay I                          | Layer Definitions                                                                                    |          |

# Pilot SHIELD

pilot embedded Systems arcHltecturE for multi-Layer Dependable solutions

SEVEN FRAMEWORK PROGRAMME

| 4 | SPD  | Consider           | ations                                                     | 40 |

|---|------|--------------------|------------------------------------------------------------|----|

|   | 4.1  | Fundame            | Fundamental Concepts4                                      |    |

|   |      | 4.1.1              | Security and Privacy                                       |    |

|   |      | 4.1.1.1            | Concepts                                                   |    |

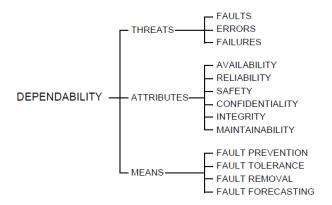

|   |      | 4.1.2<br>4.1.2.1   | Dependability                                              |    |

|   |      | 4122               | The attributes                                             |    |

|   |      | 4.1.2.2            | The means                                                  | -  |

|   | 4.2  | -                  | ed Systems                                                 |    |

|   | 716  | 4.2.1              | Introduction                                               |    |

|   |      | 4.2.2              | Design of Secure Embedded Systems                          |    |

|   |      | 4.2.2.1            | System Design Issues                                       | 45 |

|   |      | 4.2.2.2            | Application Design Issues                                  |    |

|   |      | 4.2.3              | Cryptography and Embedded Systems                          |    |

|   |      | 4.2.3.1            | Physical Security                                          |    |

|   |      | 4.2.3.2            | Side-channel cryptanalysis                                 |    |

|   | 4.0  | 4.2.3.3            | Side channel implementations                               |    |

|   | 4.3  | • •                |                                                            | 49 |

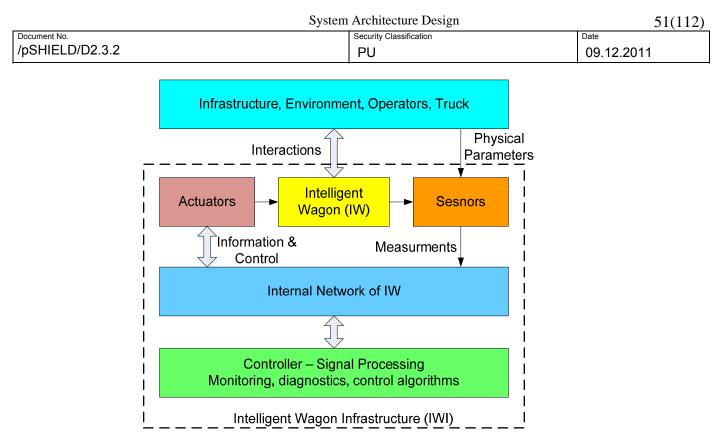

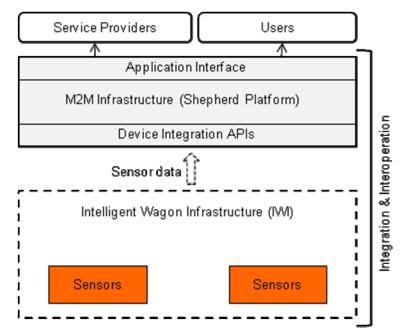

|   | 4.4  |                    | ary Concept of pSHIELD Demonstrator<br>ture                | 50 |

|   |      | 4.4.1              | System architecture for monitoring                         |    |

|   |      | 4.4.2              | System architecture for Integration and Interoperation for |    |

|   | 4 5  | 0                  |                                                            |    |

|   | 4.5  | •                  | Architecture SPD functionalities                           |    |

| 5 | SPD  | Requiren           | nents                                                      | 54 |

|   | 5.1  | System A           | Architecture Security Requirements                         | 54 |

|   | 5.2  | System A           | Architecture Privacy Requirements                          | 56 |

|   | 5.3  | System A           | Architecture Dependability Requirements                    | 56 |

| 6 | Syst | em Desig           | n                                                          | 58 |

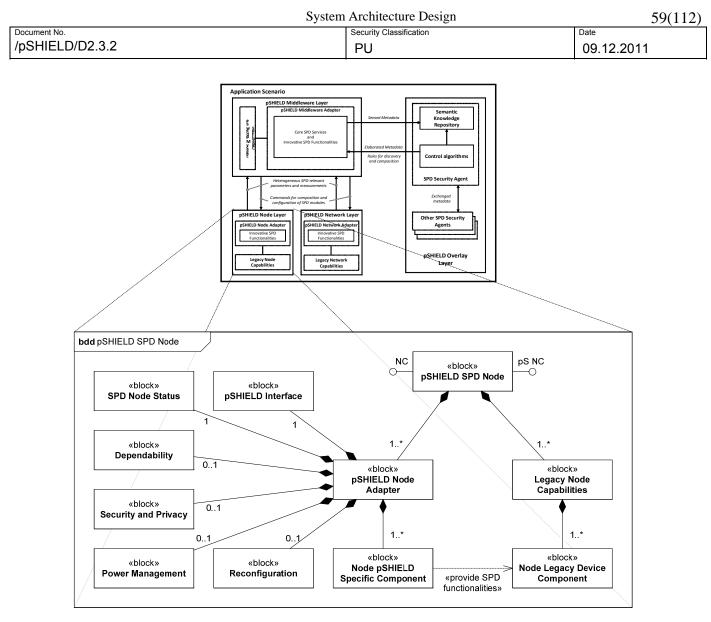

|   | 6.1  | Node Lay           | yer                                                        | 58 |

|   |      | 6.1.1              | Formal conceptual model                                    |    |

|   |      | 6.1.1.1            | Description of pSHIELD SPD Node Layer Blocks               | 60 |

|   |      | 6.1.1.2            | pSHIELD Node Layer Capabilities and Functionalities        | 62 |

|   |      | 6.1.1.3            | Intrinsic SPD capabilities                                 | 65 |

|   |      | 6.1.1.4<br>Nano no | Requirements for pSHIELD Power Node, Micro/Personal Nod    |    |

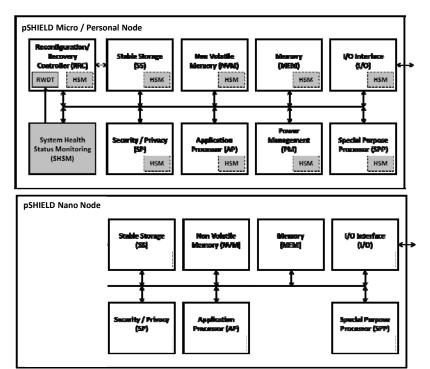

|   |      | 6.1.2              | Nano and Micro/Personal node HW/SW                         |    |

|   |      | 6.1.2.1            | Nano, Micro and Personal node description                  |    |

|   |      | 6.1.2.2            | Nano, Micro and Personal Node operating systems            |    |

|   |      | 6.1.2.3            | Specific SPD Considerations for Wireless Sensor Networks   | 72 |

7

8

# Pilot SHIELD

pilot embedded Systems arcHltecturE for multi-Layer Dependable solutions

SEVEN FRAMEWORK PROGRAMME

|            | 6.1.2.4          | SPD models for Nano, Micro and Personal nodes                | 73   |

|------------|------------------|--------------------------------------------------------------|------|

|            | 6.1.3            | Power node HW/SW                                             |      |

|            | 6.1.3.1          | Power Node software (OS, Protocol stack, Interfaces)         | 75   |

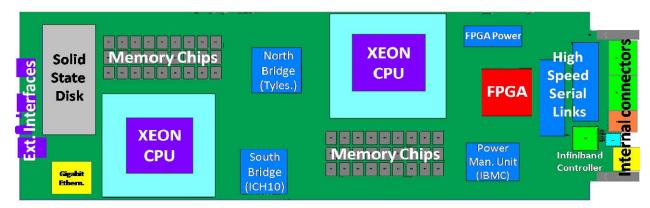

|            | 6.1.3.2          | Power Node hardware (Radio, Power, CPU, Interfaces, Sensing, |      |

|            | extras (I        | FPGA etc.))                                                  | 76   |

|            | 6.1.3.3          | Power Node Reconfigurability                                 | 78   |

|            | 6.1.3.4          | Technical Specifications                                     | 79   |

| 6.2        | Network          | Layer HW/SW                                                  | 80   |

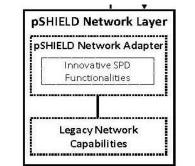

|            | 6.2.1            | pSHIELD Network Layer and pSHIELD Network Adapter            | 80   |

|            | 6.2.2            | Components and Devices                                       |      |

|            | 6.2.3            | Functions and Services                                       |      |

|            | 6.2.3.1          | Smart SPD Driven Transmission                                |      |

|            | 6.2.3.2          | Trusted and Dependable Connectivity                          |      |

|            | 6.2.3.3          | Node Performance Network Services                            | 88   |

|            | 6.2.4            | Communication protocols                                      |      |

|            | 6.2.5            | Interfaces                                                   |      |

|            | 6.2.6<br>6.2.6.1 | Security<br>Cryprographic Algorithms                         |      |

|            | 6.2.6.2          |                                                              |      |

|            | 6.2.6.3          | SSL                                                          |      |

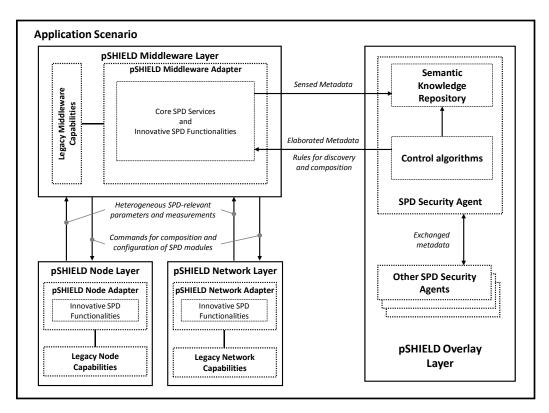

| 6.3        |                  | are Layer                                                    |      |

| 0.3        | 6.3.1            | -                                                            |      |

| <b>C A</b> |                  | Formalized conceptual model                                  |      |

| 6.4        | •                | Layer                                                        |      |

| 6.5        | •                | Overall Architecture                                         |      |

| 6.6        |                  | S                                                            | .107 |

|            | 6.6.1            | Internal                                                     |      |

|            | 6.6.2<br>6.6.3   | External                                                     |      |

|            | 6.6.4            | Node<br>Components                                           |      |

| Cond       |                  |                                                              |      |

|            |                  |                                                              |      |

| Refe       | rences           |                                                              | 111  |

# Figures

| Figure 1 – A generic embedded system structure                                                   |     |

|--------------------------------------------------------------------------------------------------|-----|

| Figure 2 - Overview of the functional architecture of TISPAN NGN release 2                       |     |

| Figure 3 - Different kinds of cross-layer design proposals (boxes represent the protocol layers) | 18  |

| Figure 4 - Proposals for architectural blueprints for wireless communications                    | 19  |

| Figure 5 - Proposed Cross-Layer Interaction Model                                                | 20  |

| Figure 6 - Cross-layer adaptation and optimization in satellite network                          | 22  |

| Figure 7 - Cross-layer architectures for indirect and direct communications                      | 23  |

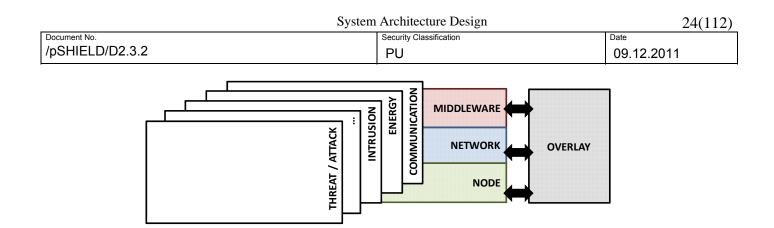

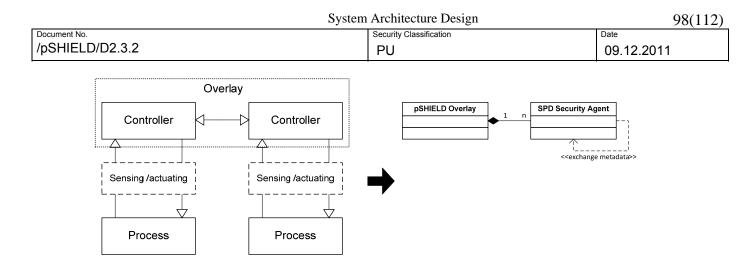

| Figure 8 – pSHIELD Overlay                                                                       | 24  |

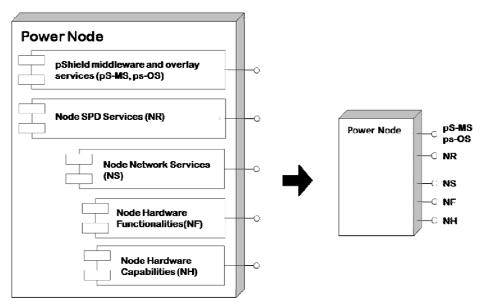

| Figure 9 – Power Node pSHIELD component                                                          |     |

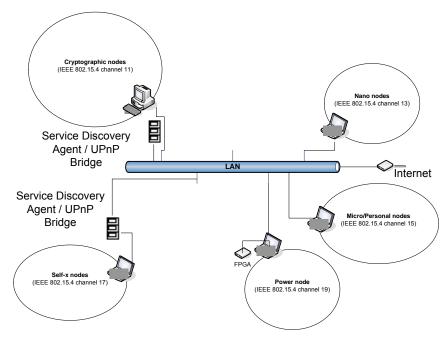

| Figure 10 - Network Layer: paradigm architecture                                                 | 31  |

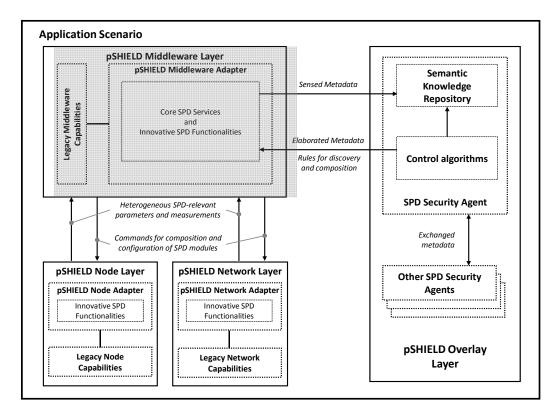

| Figure 11 – pSHIELD Middleware layer                                                             |     |

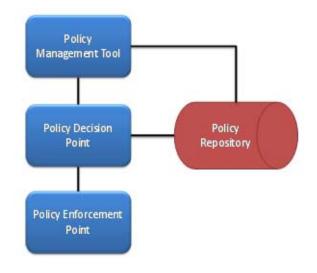

| Figure 12 – Typical IETF PBM Architecture                                                        | 37  |

| Figure 13– Dependability concept                                                                 |     |

| Figure 14 – Intelligent Wagon Infrastructure                                                     | 51  |

| Figure 15 – Integration & Interoperation concept of heterogeneous services                       |     |

| Figure 16 - Formal conceptual model of pSHIELD SPD Node Layer                                    |     |

| Figure 17 - Schematic view of SPD modules of a generic pSHIELD Nano, Micro and Personal Node     |     |

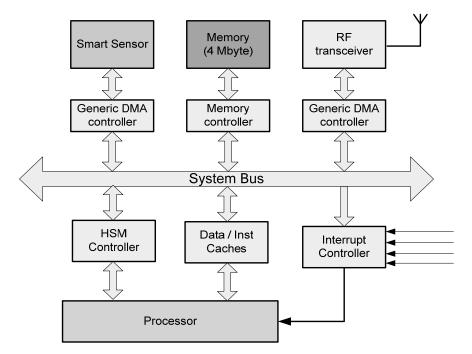

| Figure 18 - Hardware architecture and nano node chip partitioning                                |     |

| Figure 19 - Concept model for security and dependability.                                        |     |

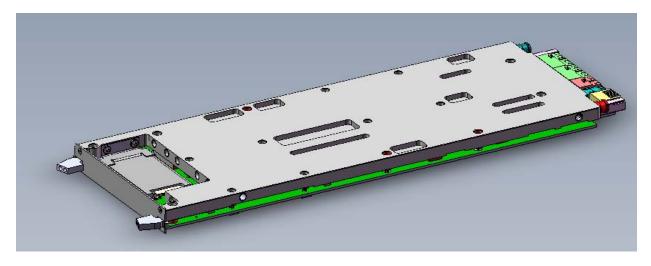

| Figure 20 - Power Node board concept, with and without cooling heat sinks                        |     |

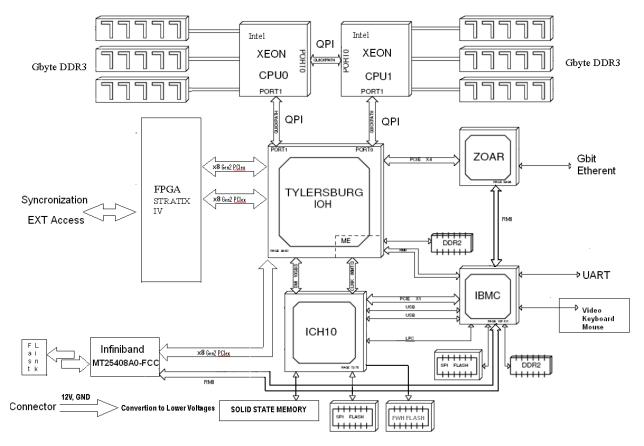

| Figure 21 - Power Node architecture: high level description                                      |     |

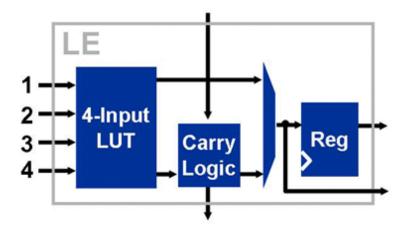

| Figure 22 – Internal structure of an FPGA logic element                                          |     |

| Figure 23 - pSHIELD Network Layer: Adapter and Legacy                                            |     |

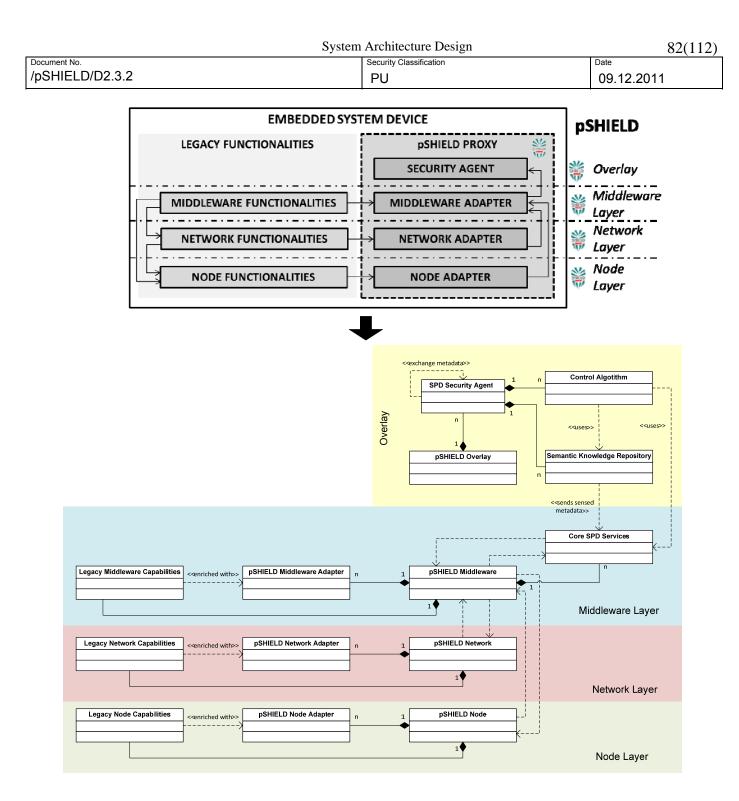

| Figure 24 - ESD and pSHIELD System layered view                                                  |     |

| Figure 25 - Intelligent Wagon internal Network                                                   |     |

| Figure 26 – Network of connected devices (M2M platform)                                          |     |

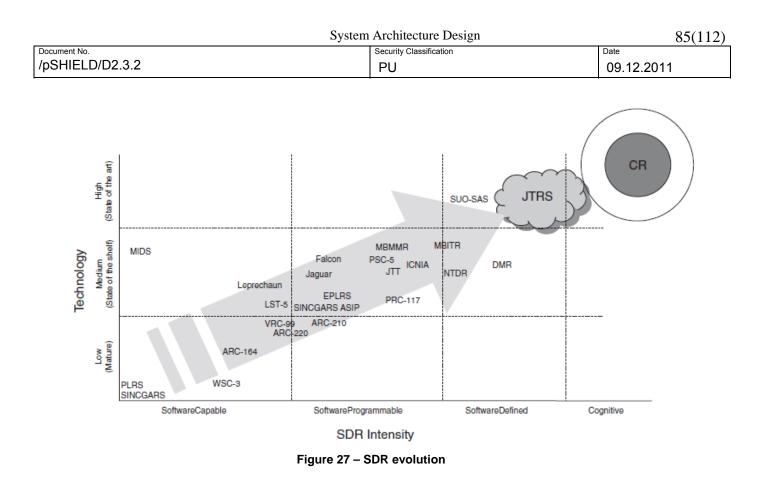

| Figure 27 – SDR evolution                                                                        |     |

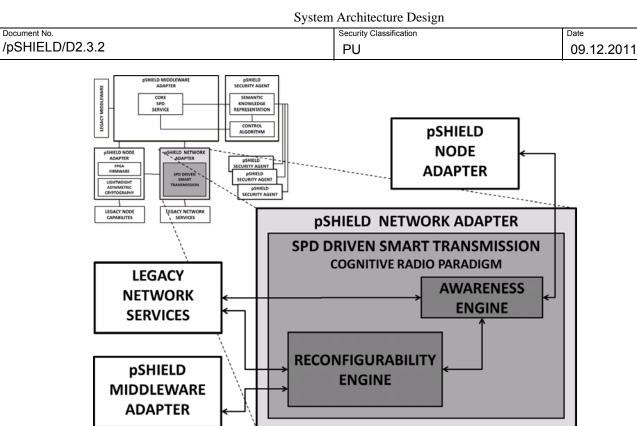

| Figure 28 – pSHIELD NETWORK ADAPTER conceptual model                                             |     |

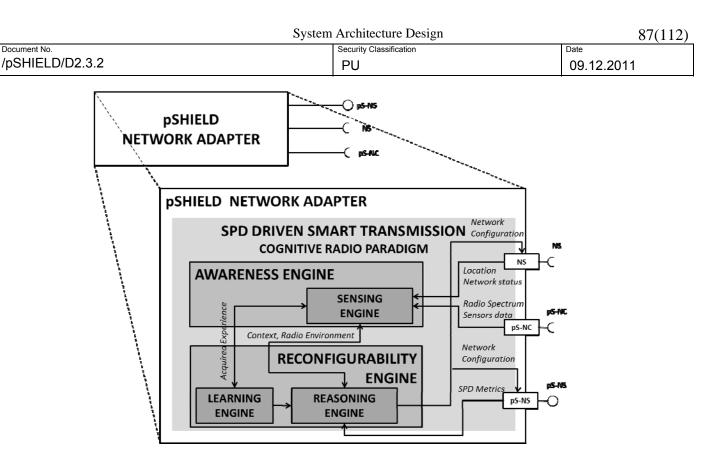

| Figure 29 – pSHIELD Network Adapter with some examples of exchanged information                  |     |

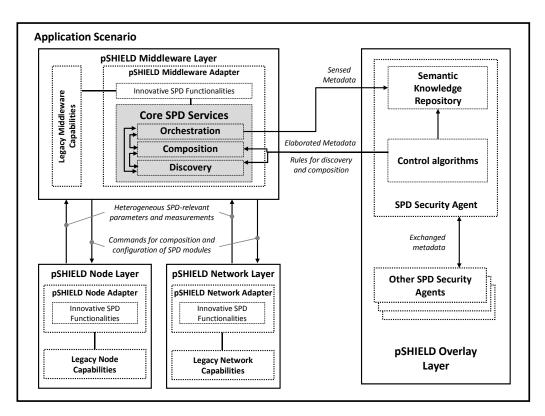

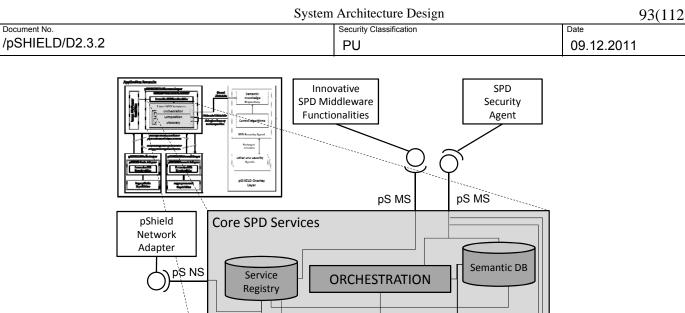

| Figure 30 – Core SPD services in the pSHIELD functional component architecture                   |     |

| Figure 31 – Core SPD services in the pSHIELD functional component architecture                   |     |

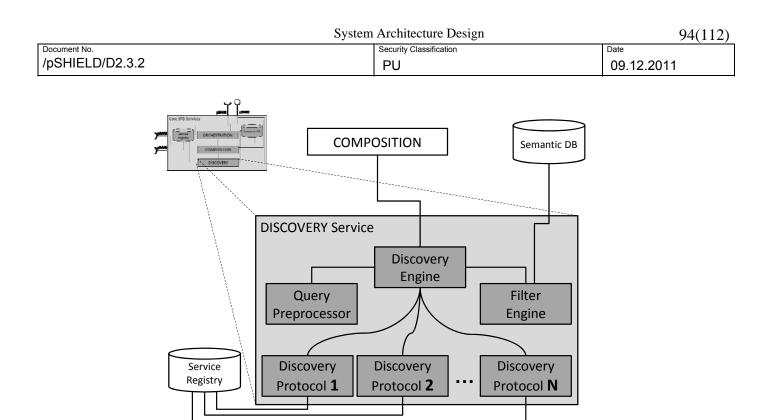

| Figure 32 – Details of the Discovery core SPD service                                            |     |

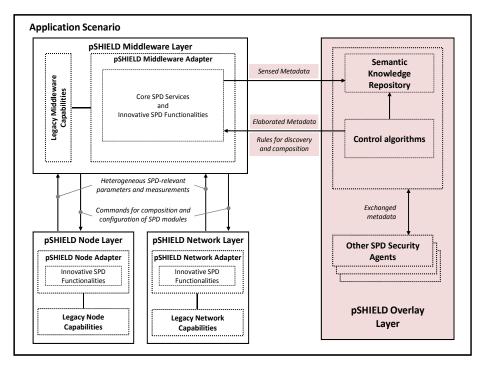

| Figure 33 – pSHIELD overlay: a functional view                                                   |     |

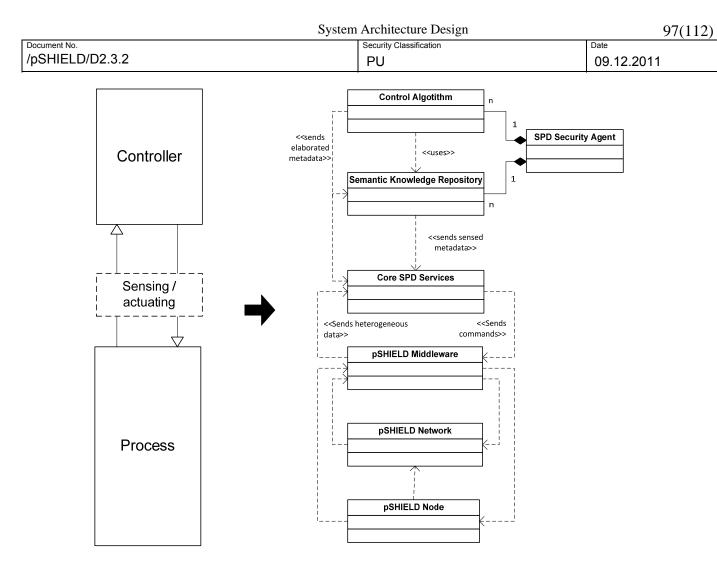

| Figure 34 – Formalized conceptual model for pSHIELD Security Agent                               |     |

| Figure 35 – Formalized conceptual model for the pSHIELD Overlay                                  |     |

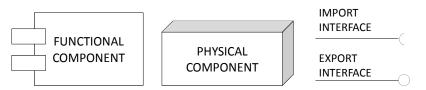

| Figure 36 – pSHIELD functional architecture formalism                                            |     |

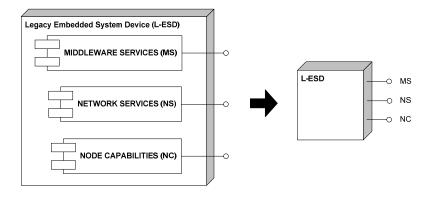

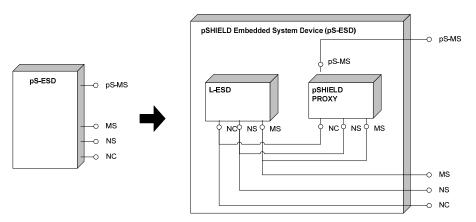

| Figure 37 – Legacy Embedded System Device (L-ESD) with its exposed functionalities               |     |

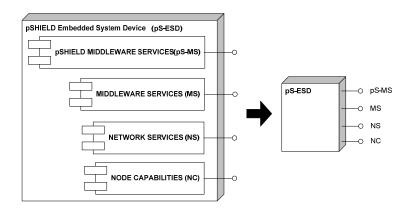

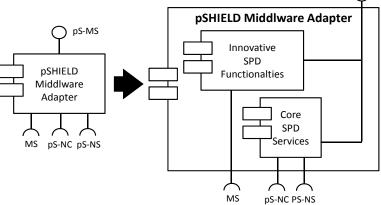

| Figure 38 – pSHIELD Embedded System Device (pS-ESD) with its exposed functionalities             |     |

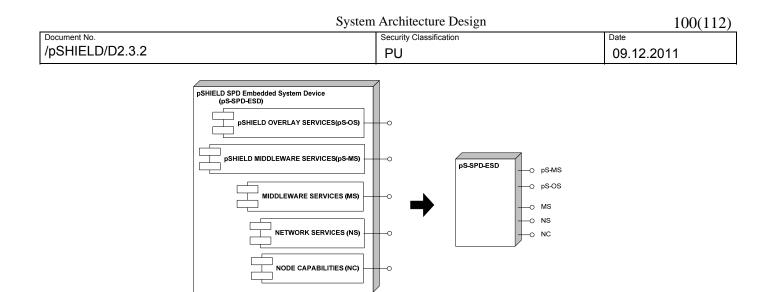

| Figure 39 – pSHIELD Embedded System Device (pS-ESD) with its exposed functionalities             |     |

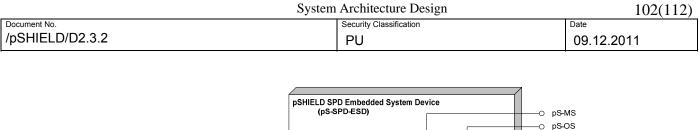

| Figure 40 – pSHIELD SPD Embedded System Device (pS-SPD-ESD)                                      |     |

|                                                                                                  |     |

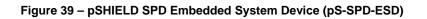

| Figure 41 – pSHIELD System Architecture decomposed into pSHIELD Subsystem                        |     |

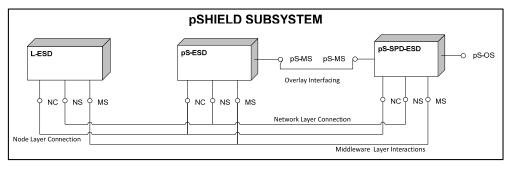

| Figure 42 – pSHIELD System Architecture highlighting the ESD types                               |     |

| Figure 43 – pS-SPD-ESD architecture                                                              |     |

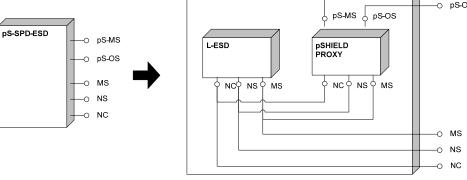

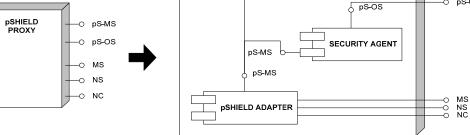

| Figure 44 – pSHIELD Proxy component architecture                                                 |     |

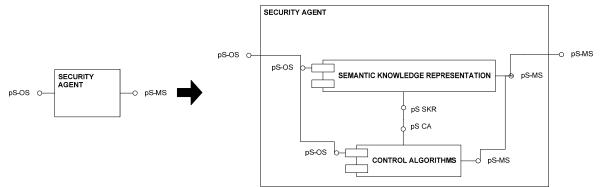

| Figure 45 – pSHIELD Security Agent component architecture                                        |     |

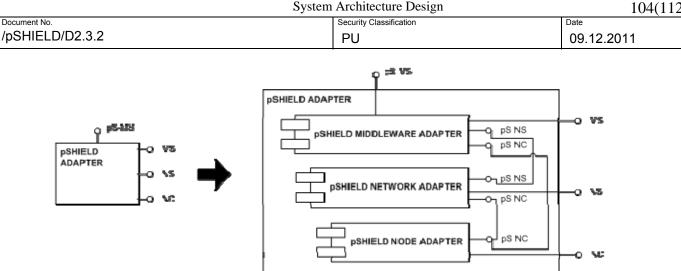

| Figure 46 – pSHIELD Adapter component architecture                                               |     |

| Figure 47 – pSHIELD Middleware Adapter component architecture                                    |     |

| Figure 48 – pS-ESD component architecture                                                        |     |

| Figure 49 – L-ESD component architecture                                                         |     |

| Figure 50 – pSHIELD functional component architecture                                            | 106 |

# Tables

| Table 1 - pSHIELD enabling technologies by node types    | 67 |

|----------------------------------------------------------|----|

| Table 2 - pSHIELD services by node types                 |    |

| Table 3 - An example of the personal node SPD components |    |

| Table 4 - Legacy Network Stack (802.11a)                 |    |

| Table 5 - Legacy Network Stack (Ethernet)                |    |

| Table 6 - IEEE 802.11 family of standards                |    |

# Glossary

| AES      | Advanced Encryption Standard                            |

|----------|---------------------------------------------------------|

| API      | Application Programming Interface                       |

| BSS      | Basic Service Set                                       |

| CCK      | Complementary Code Keying                               |

| CCMP     | Counter mode with Cipher block chaining MAC Protocol    |

| CDMA     | Code Division Multiple Access                           |

| CLA      | Cross Layer Architecture                                |

| CPU      | Central Processing Unit                                 |

| CR       | Cognitive Radio                                         |

| CSMA/CD  | Carrier Sense Multiple Access with Collision Detection  |

| DDR3     | Double-Data-Rate                                        |

| DPRAM    | Dual Ported RAM                                         |

| DRA      | Dynamic Resource Allocation                             |

| DRAM     | Dynamic RAM                                             |

| DSP      | Digital Signal Processor                                |

| DSSS     | Direct-Sequence Spread Spectrum                         |

| DVB-RCS  | Digital Video Broadcasting Return Channel via Satellite |

| EAP      | Extensible Authentication Protocol                      |

| EAP-TLS  | EAP-Transport Layer Security                            |

| EAP-TTLS | EAP-Tunneled Transport Layer Security                   |

| ESD      | Embedded System Device                                  |

| ESs      | Embedded Systems                                        |

| FDMA     | Frequency Division Multiple Access                      |

| FCC      | Federal Communications Commission                       |

| FHSS     | Frequency-Hopping Spread Spectrum                       |

| FPGA     | Field-programmable Gate Array                           |

| FSK      | Frequency-Shift Keying                                  |

| I/O      | Input/Output                                            |

| JVM      | Java Virtual Machine                                    |

## Pilot SHIELD

pilot embedded Systems arcHltecturE for multi-Layer Dependable solutions

SEVEN FRAMEWORK PROGRAMME

| LAN         | Local Area Network                          |

|-------------|---------------------------------------------|

| LDAP        | Lightweight Directory Access Protocol       |

| NGN         | Next Generation Network                     |

| OFDM        | Orthogonal Frequency-Division Multiplexing  |

| OS          | Operating System                            |

| PC          | Personal Computer                           |

| PEAP        | Protected EAP                               |

| pS-ESD      | pSHIELD Embedded System Device              |

| pS-MS       | pSHIELD Middleware Service                  |

| pS-OS       | pSHIELD Overlay Service                     |

| pS-P        | pSHIELD Subsystem                           |

| pS-P        | pSHIELD Proxy                               |

| pS-SPD-ESD  | SPD Embedded System Device                  |

| PSK         | Phase-Shift Keying                          |

| QoS         | Quality of Service                          |

| RAM         | Random Access Memory                        |

| RF          | Radio Frequency                             |

| SA          | Security Agent                              |

| SDR         | Software Defined Radio                      |

| SDRAM       | Synchronous Dynamic RAM                     |

| SIP         | Session Initiation Protocol                 |

| SNMP        | Simple Network Management Protocol          |

| SPI         | Serial Peripheral Interface                 |

| SOA         | Service Oriented Architecture               |

| SPD         | Security Privacy Dependability              |

| SSL         | Secure Socket Layer                         |

| TDMA        | Time Division Multiple Access               |

| TKIP        | Temporal Key Integrity Protocol             |

| TPM         | Trusted Platform Module                     |

| UART        | Universal Asynchronous Receiver/Transmitter |

| UCS         | Use case Scenario                           |

| USB         | Universal Serial Bus                        |

| VPN         | Virtual Private Network                     |

| WEP         | Wired Equivalent Privacy                    |

| WLAN        | Wireless Local Area Network                 |

| WPA         | Wi-Fi Protected Access                      |

| WPAN        | Wireless Personal Area Network              |

| WRAN        | Wireless Regional Area Network              |

| WS-Security | Web Services Security                       |

K

# **1** Executive Summary

D2.3 is a deliverable inside pSHIELD WP2, "Scenarios, requirements and system design", separated into internal intermediate deliverable D2.3.1, "Preliminary system architecture design" and public final deliverable D2.3.2, "System architecture design". As denoted by its title, the main objective is to describe a formal and conceptual overall system architecture, to address Security, Privacy and Dependability (SPD) in the context of Embedded Systems (ESs) as "built in" rather than as "add-on" functionalities, proposing and perceiving with this strategy the first step towards SPD certification for future ESs. The methodology adopted concerns the gradual process and interaction with the major project topics, which form the framework for the architecture design, such as requirements, application scenario, metrics and technology development in the four layers described in the project. The latter, hierarchically ascending, Node, Network, Middleware and Overlay layers comprise the pSHIELD proposal, an alternative to classical layered OSI model structure. Therefore, the concluding complete architecture is presented through the definition of the four layers, the interfaces between them and the overall framework synthesized.

| Document No. Security Classification | Data            |

|--------------------------------------|-----------------|

| /pSHIELD/D2.3.2 PU                   | Date 09.12.2011 |

# 2 Introduction

The main goal of pSHIELD is to ensure that security, privacy and dependability (SPD) in the context of integrated and interoperating heterogeneous services, applications, systems and devices. Systems and services must be robust in the sense that an acceptable level of services is available despite the occurrence of transient and permanent perturbations such as hardware faults, design faults, imprecise specifications and accidental operational faults.

The pSHIELD architecture composability relies on the so called SPD modules. Indeed the pSHIELD architecture is composed by a mosaic of innovative SPD functionalities, each one of the considered layers. The pSHIELD architecture is able to derive application instantiations of the general framework, selecting statically (at design time) and dynamically (at runtime) the best SPD functionalities for achieving the required SPD levels. In particular, referring to the abovementioned layers, the SPD modules will implement the following functionalities:

- At node layer, intelligent hardware and firmware SPD

- At network layer, secure, trusted, dependable and efficient data transfer based on selfconfiguration, self-management, self-supervision and self-recovery

- At middleware layer, secure and efficient resource management, inter-operation among heterogeneous networks

- At overlay layer, composability •

R&D for embedded security, intended as a system issue that must be solved at all abstraction levels (protocols, algorithms, architecture), will lead, in the framework of this task, to a coherent, composable and modular architecture for a flexible distribution of SPD information and functionalities between different ESs while supporting security and dependability characteristics.

This framework in D2.3.2 aims, at the one hand, to explore the minimum set of interdependencies between applications and architectures in an efficient way and to systematically classify those with respect to SPD. On the other hand, it aims to produce a composable architecture which will include most critical elements, thus covering most of the SPD requirements for all the applications. This approach is expected to produce a multi-layered architecture, where each layer consists of several hardware and software SPD modules (components), since it is imperative to take into account the need for composable security, privacy and dependability.

The resulting architecture has to be reconfigurable, offline, meaning that mechanisms should be provided to the designer for enabling/disabling nodes in order to tailor the overall system to his needs. Furthermore, fault diagnosis and fault recovery have to be addressed both in hardware and software layers.

Intra-layer and inter-layer interfaces should be defined in the system architecture to ensure the correct communication among the different SPD modules.

| System          | Architecture Design     | 13(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

# **3** Terms, Definitions and Approaches

- (1) Embedded System (ES) is a computer system designed to perform one or a few dedicated functions often with real-time computing constraints. It is embedded as part of a complete device often including hardware and mechanical parts. By contrast, a general-purpose computer, such as a personal computer (PC), is designed to be flexible and to meet a wide range of end-user needs.

- (2) An Embedded System is a microprocessor based system that is embedded as a subsystem, in a larger system (which *may or may not be a computer system*).

In general, "embedded system" is not a strictly definable term, as most systems have some elements of extensibility or programmability. For example, handheld computers share some elements with embedded systems such as the operating systems and microprocessors which power them, but they allow different applications to be loaded and peripherals to be connected. Moreover, even systems which do not expose programmability as a primary feature generally need to support software updates. On a continuum from "general purpose" to "embedded", large application systems will have subcomponents at most points even if the system as a whole is "designed to perform one or a few dedicated functions", and is thus appropriate to call "embedded".

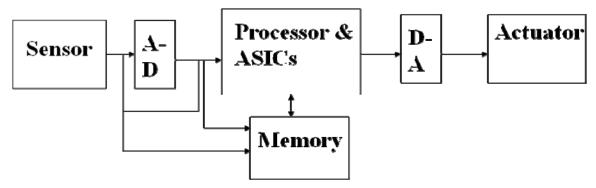

An ES is some combination of computer hardware and software, either fixed in capability or programmable, that is specifically designed for a particular function. Industrial machines, automobiles, medical equipment, cameras, household appliances, airplanes, vending machines and toys (as well as the more obvious cellular phone and PDA) are among the myriad possible hosts of an embedded system. For example, the following figure shows the essential parts of an ES:

- Microprocessor / DSP

- Sensors

- Converters (A-D and D-A)

- Actuators

- Memory (On-chip and Off chip)

- Communication path with the interacting environment

Figure 1 – A generic embedded system structure

**Embedded Device** (ED) can be a small programmable chip that can be programmed to execute certain functions.

**Heterogeneous system** is a group of interacting, interrelated, or interdependent elements forming a complex whole.

Heterogeneous device integration designates technologies that can be integrated on one platform device.

| System          | Architecture Design     | 14(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

**Heterogeneous network** is a network connecting computers and other devices with different operating systems and/or protocols.

**Architecture**: The architecture of a system defines its basic components and important concepts and describes the relationships among them.

**Functional architecture (FA)**: The functional architecture can be viewed as the set of basic information processing capabilities available to an information processing system. The functional architecture is comprised of a set of primitive operations or functions. This means that these basic functions cannot be explained by being further decomposed into less complex ("smaller") sub-functions.

The functional architecture is constructed from an analysis of different functional requirements as deduced from different use cases.

#### Example 1:

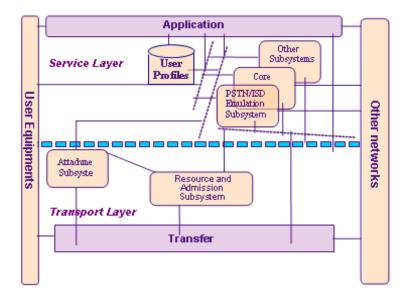

Figure 2 shows one example of NGN functional architecture.

Figure 2 - Overview of the functional architecture of TISPAN NGN release 2

The main scope of the above functional architecture is to identify a set of functional blocks, for example: Media Gateway Function (MGF); Border Gateway Function (BGF); Access Relay Function (ARF); Signaling Gateway Function (SGF); Media Resource Function Processor (MRFP); Layer 2 Termination Function (L2TF), etc. Each subsystem is specified as a set of functional entities and related interfaces. As a result implementers may choose to combine functional entities where this makes sense in the context of the business models, services and capabilities being supported. Where functional entities are combined the interface between them is internal, hidden and un-testable.

#### Example 2:

The Web system architectures have a technical architecture that is divided in functional and information architecture. For both the information architecture and the functional architecture, various abstraction levels exist, which include the business architecture, logical architecture, physical architecture and implementation architecture:

| System          | Architecture Design     | 15(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

- Business Architecture: The business architecture represents business processes, policies and procedures, workflows and user interactions. This is used to guide the design of other more technical related architecture layers

- Logical Architecture: The logical architecture defines at a high level the structure of the system to be developed. The elements in this layer are logical concepts, instead of concrete or physical software components

- *Physical Architecture*: The physical architecture further defines the technical solution at a detailed level. Some design decisions, such as the selection of content storage product, can be represented in this layer

- *Implementation Architecture*: The implementation architecture specifies system composition and interconnections

**pSHILED Functional Architecture (pSFA)** is composed by four functional layers: node, network, middleware and overlay, which represent a set of four functional sub-systems that are specified by its set of elements, functional entities and interfaces.

**Node Layer (NoL) of pSFA**: node layer is composed of Intelligent ES HW/SW Platform and have different kinds of Intelligent ES Nodes: nano node, micro/personal node, power node, and Dependable Self-X Crypto Technologies. This layer is composed of standalone and/or connected NoL elements like sensors and actuators, which perform smart transmission.

The NoL is a layer composed by physical nodes (i.e. hardware). Each node is a generic Embedded System (for example a sensor, an actuator, a transmitter etc.). The functionality of the NoL:

**Network Layer (NeL) of pSFA** is a heterogeneous layer composed by a common set of protocols, procedures, algorithms and communication technologies that allow the communication between two or more nodes.

**Middleware Layer (ML) of pSFA** is the software layer that provides the basic functionalities to use the underlying networks of embedded systems (like service discovery and composition) as well as some security functionalities (like accounting or access control). This layer, being software, is installed on the nodes.

**Overlay Layer (OL) of pSFA** is a logical vertical layer that collects (directly or indirectly) semantic information coming from the Node, Network and Middleware layers and uses them to compute the adequate actions (if any) that ensure the desired level of SPD. It is a software routine running at middleware and/or application level.

### 3.1 Cross-Layer / Cross-Overlay Architecture Definitions

#### 3.1.1 Introduction

The purpose of this chapter is to give an overview on the cross-layer architectures (CLA) proposed recently by the research community and to address in details SPD issues for overall pSHIELD System Architecture (pSSA).

In wireless and mobile networking envisioned for pSHIELD System Architecture (pSSA), difficult environmental conditions are a permanent challenge, resulting in a demand for cross-layer optimizations. There is also a need to further increase flexibility of the network. Therefore, we believe cross-layer architectures should adapt themselves to these changing conditions, just as they adapt the network stack, devices, and applications.

The network protocol stacks are logically organized in layers. These layers are strictly separated and the cross-layer functionality between them is restricted by determined interfaces, which in effect only allow passing packets up and down the stack. In principle, all these layers have been designed to fulfil

| System          | Architecture Design     | 16(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

their functionality without interaction across the layers. History shows that this works well in wired and static environments. Popularity and success of wireless networks and highly mobile nodes is currently dominating in new development and research activities. In order to adapt to the rapidly and frequently changing network conditions under those circumstances, a more sophisticated interaction between protocols than in a traditional layered architecture is desirable. The existing solutions are not able to dynamically change which of these to use and how to use them, i.e., the adaptation, reparameterization and addition of cross-layer optimizations during runtime. Moreover, customization of optimizations in existing frameworks is often cumbersome and complicated, if it can be done at all.

Cross-layer architectures diverge from the existent network design approaches, where each layer of the protocol stack operates independently and the data between the successive layers is exchanged in a very strict and systematic manner. There are several advantages of a layered approach since modularity, robustness and ease of design are effortlessly achieved. The modularity that the layers provide allows for

potential arbitrary combination of protocols and the maintainability is being improved as new versions of a protocol can be inserted without having to alter the rest of the network stack. However the properties of the different layers have substantial interdependencies and a modularized design may be suboptimal with regards to performance especially in satellite and mobile wireless environments, where the communication channels and traffic patterns are more unpredictable than in wired-line networks.

There has been much talk about cross-layer design for wireless communication networks lately. It has been argued repeatedly that layer boundaries, as specified in the layered architectures, are not suitable for wireless communications and performance gains can be made by giving up strict layering to do cross-layer design [1], [2].

This chapter discusses a communication methodology involving node cooperation which, while demonstrating a new opportunity created by wireless networks, significantly challenges the layered architecture.

Cross-layer design touches not just communications and networking, but is also intimately connected to concepts related to communications architecture. Layered architectures have served to make the protocol design activity systematic and modular. Potential performance gains can always motivate a designer to not follow the layered architectures and do cross-layer design. But cross-layer design cannot be seen as an end itself.

This chapter presents both, a state-of-the-art (SoA) of the ongoing work and platforms over which new research can be built [3]-[20]. In this project we will discuss specific cross-layer design proposals and new alternatives. But mainly, we encourage a more holistic treatment of cross-layer design itself.

We therefore propose a Cross-Layer pSHIELD System Architecture (CLA-pSSA) with the following properties:

- Signalling between an arbitrary amount of layers and system components

- Extensibility of the architecture and adaptability of optimizations at runtime

- High usability for cross-layer developers via an abstract description language for optimization rules

There also exist several cross-layer architectures facilitating signalling across all layers, i.e. any-toany layer signalling. For example, Cross-Layer Signalling Shortcuts (CLASS) enables direct signalling between all layers by message passing [8].

#### 3.1.2 Description of Cross-Layer Architecture

#### 3.1.2.1 A definition for Cross-Layer Design (CLD)

A layered architecture, like the seven layer Open Systems Interconnection (OSI) model [3], defines an hierarchy of services to be provided by the individual layers. The services at the layers are realized by

| System          | Architecture Design     | 17(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

. . . . . . .

designing protocols for the individual layers, which can be implemented on the target platform to obtain a complete system.

At the protocol design phase, the designer has two choices. Protocols can be designed by respecting the rules of the original architecture. In the case of the layered OSI reference model, this would mean designing protocols such that they only make use of the services at the lower layers and not be concerned about the details of how the service is being provided. It also implies that the protocols would not need any interfaces that are not present in the reference architecture.

Alternatively, protocols can be designed by violating the reference architecture. Since the reference architectures in communication and networking have traditionally been layered, its violation is generally termed as cross-layer design.

#### 3.1.2.2 A taxonomy of CLD

In recent times, a large number of cross-layer designs have been proposed. A classification based on the layers that are coupled by the different proposals can be found in [4]. In this section, we classify the existing cross-layer design proposals according to the kind of architectural violations they represent. Two points should be mentioned here. Firstly, our coverage of the cross-layer design proposals is meant to be representative and not exhaustive. Secondly, the reference architecture we assume is motivated from the "best of both worlds" five-layer model proposed in [5]. Thus, we assume that the reference architecture has the application layer, the transport layer, the network layer, the link layer which comprises the data-link control (DLC) and medium access control (MAC) sub-layers [3], and the physical layer—with all the layers performing their generally understood functionalities.

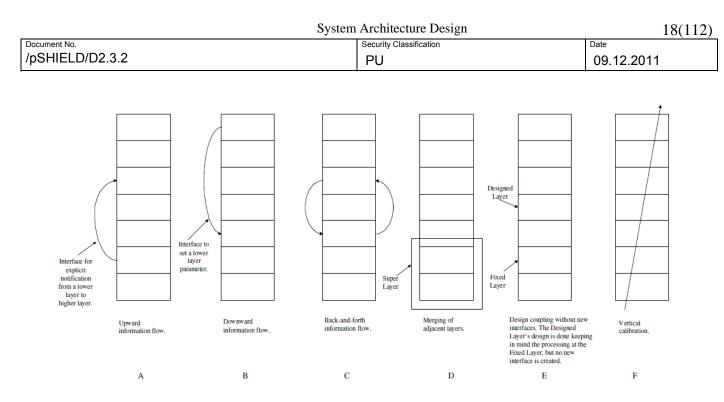

We identify the following architectural violations:

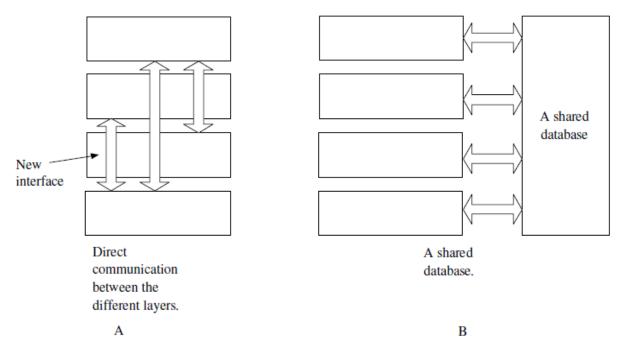

- 1) Creation of new interfaces (Figure 3: A, B, C)

- 2) Merging of adjacent layers (Figure 3: D)

- 3) Design coupling without new interfaces (Figure 3: E)

- 4) Vertical calibration across layers (Figure 3: F)

#### A. Creation of new interfaces

Several cross-layer designs require creation of new interfaces between the layers. These can further be divided into three categories depending on the direction of information flow along the new interfaces:

- *1)* Upwards: From lower layer(s) to a higher layer

- 2) Downwards: From higher layer(s) to a lower layer

- 3) Back and forth: Iterative flow between the higher and lower layer

We now discuss the three sub-categories in more detail and point out the relevant examples.

- 1) Upward information flow: A higher layer protocol that requires some information from the lower layer(s) at runtime results in the creation of a new interface from the lower layer(s) to the higher layer, as shown in Figure 3 A

- 2) Downward information flow: Some cross-layer design proposals rely on setting parameters on the lower layer of the stack at run-time using a direct interface from some higher layer, as illustrated in Figure 3 B. Such downward flow of information is termed as Hints in [6]. As an example, the applications can inform the link layer about their delay requirement and the link layer can then treat packets from the delay sensitive applications with priority [7]

- 3) Back and forth information flow. Two layers, performing different tasks, can collaborate with each other at run-time. Often, this manifests in an iterative loop between the two layers, with information flowing back-and-forth between the layers, as highlighted in Figure 3 C

Figure 3 - Different kinds of cross-layer design proposals (boxes represent the protocol layers)

#### 3.1.2.3 Existing and new CLAs

#### 3.1.2.3.1 A classic CLA

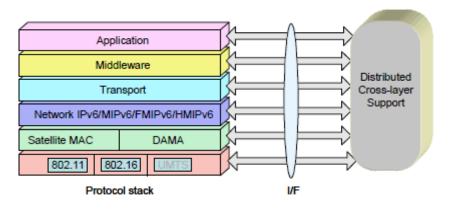

Cross-layer design proposals that we looked at in Section 3.1.2.2 demonstrate the violation of layered architectures at the protocol design phase itself. Hence, a question that naturally comes up is, "Can there be architectures that are general enough such that protocols for wireless networks can be designed without violating them?" In fact, this is a complicated question. Determining what the new architectures should look like requires the study of not only the performance issues from a communication or networking viewpoint, but also an understanding of the implementation related issues. Nevertheless, some preliminary proposals have been made in the literature. These can be put into two categories:

- 1) Allowing the layers to communicate with each other (Figure 4 2A)

- 2) A shared database across the layers (Figure 4 B)

#### A. Allowing the layers to communicate

A straightforward way to allow information sharing between the layers is to allow them to communicate with each other, as depicted schematically in Figure 4 A. Practically speaking this means making the variables at one layer visible to the other layers at run-time. Notice that under strictly layered architectures, every layer manages its own variables and its variables are of no concern to other layers.

There are many ways in which the layers can communicate with one another. For instance, protocol headers may be used to allow flow of information between the layers. Alternatively, the extra "interlayer" information could be treated as internal packets. The work in [8] presents a comparative study of several such proposals and goes on to present another such proposal, namely, the Cross-layer signalling shortcuts (CLASS).

CLASS allows any two layers to communicate directly with one another. Similarly, the Hints and Notifications proposal discussed in [6] makes network layer the hub of inter-layer communication. These proposals are appealing in the case where just a few cross-layer information exchanges are to be implemented in systems that were originally designed in conformance with the layered architectures. In that case, one can conceivably "punch" a few holes in the stack while still keeping it tractable. However, in general, when variables and internal states from the different layers are to be

| System          | Architecture Design     | 19(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

shared between the different layers as prescribed by such proposals, a number of implementation issues relating to managing shared memory spaces between the layers may need to be resolved.

#### B. Shared database across the layers

The other architecture proposal recommends a common database that can be accessed by all the layers, as illustrated in Figure 4 B. See for instance references [9] and [4]. In one sense, the common database is like a new layer, providing the service of storage/retrieval of information to all the layers.

The shared database approach is particularly well suited to vertical optimizations. An optimization program can interface with the different layers at once through the shared database. The main issue here is the design of the interactions between the different layers and the shared database.

Figure 4 - Proposals for architectural blueprints for wireless communications

#### 3.1.2.3.2 New CLA

#### 3.1.2.3.2.1 Cross-Layer Interaction Model

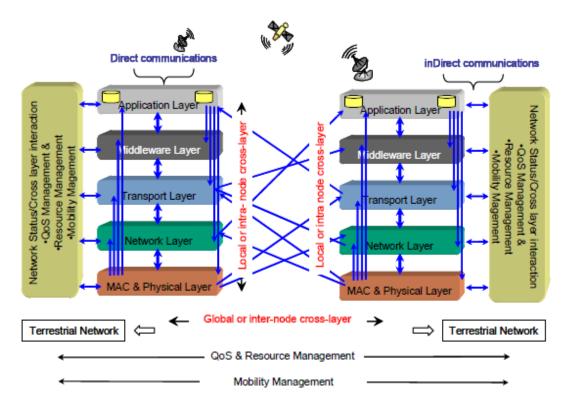

The cross-layer architectures proposed in the literature do not address all the design goals of interoperability, rapid prototyping, maintainability, portability and efficiency. Starting from this consideration, the goal of this work is to provide a generic framework for building and organizing a cross-layer interactions model (CLIM) which could serve as a unified and simple way to implement cross-layer optimizations (see Figure 5). When using CLIM, the concept of NF (Network Feature) should also be introduced. A NF is either a functional service that can be provided to the end-user (e.g. QoS), or a network component whose operations/configurations are supposed to be critical in terms of performance, efficiency or services, at the system level or for the user satisfaction. Basically, cross-layer interactions may be local to or distant within a network node.

In many cases only two elementary NF are involved in the adaptation and interaction (one source NF, one target NF). In some other cases multiple (local or distant) entities could participate. Local

| System          | Architecture Design     | 20(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

communications between protocols of non-neighbour layers are done through a local interface that must be defined.

#### CLIM / Cross-layer Interaction Module

- · indirect communications model

- · distributed cross-layer support

#### Figure 5 - Proposed Cross-Layer Interaction Model

The cross-layer architecture and interaction module CLIM has two main components: 1) QoS and Resource Management and 2) Mobility Management. The QoS and Resource Management component includes:

- SIP and MAC cross-layer interactions used to support the interworking between WiMAX and DVB-RCS and multimedia QoS-aware application

- Transport layer and MAC cross-layer interaction (i.e. the interaction between TCP PEP (Performance Enhancing Proxy) and DAMA (Demand Assignment Multiple Access) in the MAC) designed to optimize the way in which the available resources is used taking into account QoS mapping at the MAC layer and enabling data to be sent to the lower layers at the speed at which the MAC layer queues are emptied (flow-control)

- IP and MAC scheduling interaction implemented in a way that can fully take advantage of QoS capabilities offered by the satellite system

- MAC and Physical layer interaction between DRA and DAMA as information in the frame constitution

The Mobility Management component utilizes a slightly modified model (CLIM-m) based on the more generic CLIM architecture together with ideas from [17][18]. The mobility management modules include:

- Algorithms for handover prediction and decision algorithms for fast handover with handover preparation, handover coordination and optimization algorithms for best performance

- Information to decide the appropriate time to initiate and execute the handover procedures

The proposed cross-layer platform for mobility management specifies a Cross-layer Manager consisting of a Link Information Manager and a Handover Manager connected to Layer Agents (LA). The Handover Manager communicates with multiple protocol layers via the LAs which capture specified parameters in each layer when the respective values are changing beyond a certain threshold. These data are reported to the Handover Manager to collect sufficient information for the Handover Decision Unit.

| System          | Architecture Design     | 21(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

#### 3.1.2.4 Challenges

There are additionally several open questions, some of which cannot be addressed from a performance viewpoint alone and require a consideration of architectural concerns too. For example:

- What should be the role of the physical layer in wireless networks?

- Is the conventional view of the network—that of a collection of point-to-point links— appropriate for wireless networks?

- How do the different cross-layer design proposals co-exist with one another?

- Will a given cross-layer design idea possibly stifle innovation in the future?

- What are the cross-layer designs that will have the most significant impact on network performance, and hence should be most closely focused on?

- Has a given design proposal been made with a thorough knowledge of the effect of the interactions between the parameters at different layers on network performance?

- Under what network and environmental conditions can a particular cross-layer design proposal be invoked?

- Can the mechanisms/interfaces used to share information between the layers be standardized?

- How do we make sure that the new architectures allow innovative usage of the wireless medium that we are likely to see in the future?

We will investigate at some of these issues in greater detail.

#### 3.1.2.5 Description of Layers

#### 3.1.2.5.1 Physical Layer

In wired networks, the role of the physical layer has been rather small—that of sending and receiving packets when required to do so from the higher layers. As we have seen, advances in the signal processing at the physical layer can allow it to play a bigger role in wireless networks. Consider, for instance, multi-packet reception capability at the physical layer.

#### 3.1.2.5.2 MAC Layer

The MAC layer's functionality is intimately connected to the network layer (and hence to the rest of the stack), we see that signal processing advances at the physical layer promise to have a significant impact on all aspects networking protocol design. Cross-layer designs relying on advanced signal processing at the physical layer are an interesting research ground for the future.

#### 3.1.2.5.3 Cross-Layer Principles

The solutions for cross-layer adaptation seek to enhance the performance of the system by jointly optimizing the performance of single or multiple cross-layers. The uncertainty is to what extent the layered architecture needs to be modified in order to introduce co-operations among protocols belonging to different layers. At one end, solutions based on triggers between the layers implement interdependencies between protocols while maintaining compatibility with strict layering. A full cross-layer design represents the other extreme; this implies introducing stack-wide layers' interdependencies that enable the optimization of each protocol's performance by exploiting the full knowledge of the network status abstracted at different layers of the protocol stack.

| System          | Architecture Design     | 22(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

However, in a multiple-objective optimization scenario, care should be taken to avoid undesirable (and unpredictable) interactions across parameters in various layers, leading to conflicts or even loops between the layers. There also exists a design trade-off between the multiple optimization goals and the effect of the increased processing and interactions to achieve these goals. Unfortunately by doing cross-layer design in an undisciplined way, it is likely to end with a poorly structured system and to greatly increase the complexity of an already complex system [10][11].

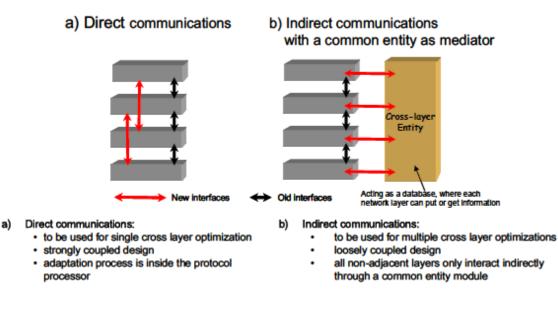

Figure 6 illustrates the main ideas of cross-layer adaptation and optimization in a hybrid terrestrial and satellite network. Cross-layer optimization may be implemented locally (intra-node) or globally (internode). A number of cross-layer methods and architectures have been proposed in the literature [12][13][14] [15][16]. They all share some common features and diverge notably in the way the crosslayer principle is implemented, on what kind of application they focus, in the capacity the architecture has and where the actual adaptation intelligence is located.

Figure 6 - Cross-layer adaptation and optimization in satellite network

These architectures mostly fit out into one of the two categories: direct or explicit cross-layer communications and indirect or implicit cross-layer communications via a common entity, see Figure 7.

| System          | Architecture Design     | 23(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

#### Two alternative approaches

Figure 7 - Cross-layer architectures for indirect and direct communications

The first category, direct communications, should be used when only a single cross layer optimization is planned. The second category, indirect communications, is realized with a common cross-layer entity or cross-layer manager, which acts as a mediator between the layers. The cross-layer entity includes a network status component of the stack that interfaces the different layers between themselves and acts as a database where each network layer can put or get information. This architecture should be used for multiple cross layer optimizations.

# 3.1.3 The Overlay as a Cross-Layer Security Architecture for Security, Privacy and Dependability

As we have seen in the previous section, a Cross-Layer Architecture is a design paradigm that could improve the performance of a generic system by simply allowing information exchange among the layers. This approach has been widely described for Telecommunication environment, however for the purpose of the pSHIELD project we need to adapt it to a different context by addressing two main issues:

i) while classical Cross-Layer is applied to the seven, well known, ISO/OSI layers, pSHIELD Cross-Layer is applied to three heterogeneous and complex layers named Node (the hardware), Network (the interconnection between nodes) and Middleware (the software services located between the hardware and the applications providing the core SPD functionalities)

ii) while classical Cross-Layer aims at optimizing telecommunication quality of service performances (like bandwidth, transmission delays and so on), the pSHIELD Cross-Layer is in charge of addressing Security, Privacy and Dependability to bring them to a reference, desired value. With Security, Privacy and Dependability we refer to a wide set of functionalities relevant for the system like Authentication, Cryptography, Authorization, Key management, Auditing, etc. For any possible threat, pSHIELD acts as a SPD overlay, applying a functional-cross-layer approach, as depicted below:

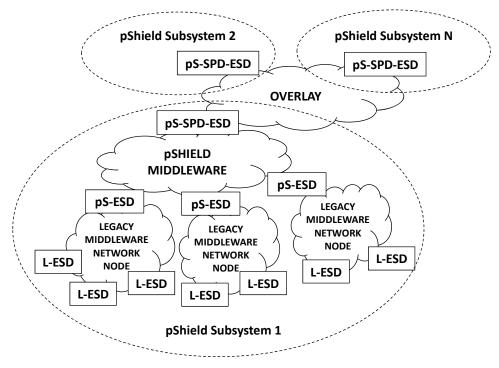

Figure 8 – pSHIELD Overlay

Given a threat or an attack (such as intrusion, tampering, energy shortage, communication fault, etc.) it potentially impacts all middleware, network and node layers. To face this threats and attacks, traditional approaches are to defend each single functionality or each single layer, without any coordination with the rest of the involved system. To ensure such an holistic approach it is necessary a Cross-Layer element to serve as a glue between the different domains (node, network and middleware). The Overlay monitors and controls the SPD level of the whole system.

In order to simplify the description, in the unfolding of the document we will refer to the "pSHIELD Cross-Layer Architecture for Security, Privacy and Dependability" with the word "Overlay Layer" or pSHIELD Overlay".

Since there are many SPD functionalities positively affected by the introduction of an Overlay layer, most of them depending on the application scenario, it is not possible to provide in advance an extensive, quantitative description of the advantages for each SPD functionality. However in the following sections some examples are provided to better understand the Overlay impact on improving the SPD level of a given system of embedded systems.

#### 3.1.3.1 Security

The Overlay approach could improve the security of an interconnected set of Embedded Systems by leveraging the basic security functionalities of each hardware and/or software components. For example if an encryption algorithm is required to protect the output of a node, the overlay could decide to perform it directly at node level (by activating the adequate chip and producing an already encrypted output) as well as at network level (by ciphering the information while transmitting it over a secured channel) or at middleware level (by ciphering the information stored in memory before sending it). Of course these solutions are equivalent if and only if they all fit the application needs.

#### 3.1.3.2 Dependability

An intuitive example of Dependability functionality that could be guaranteed by the pSHIELD overlay could be the power consumption of the system. If we consider, for example, a monitoring system composed by different nodes, communication protocols and software components, the Overlay could dynamically choose the less expensive (in terms of energy) configuration of devices or transmission protocols and active services in order to maximize the life of the battery and consequently the dependability of the system itself.

### 3.2 Node Layer Definitions

#### 3.2.1 Nano and Micro/Personal Node

Nano- and micro- sensor technology encompasses the family of devices in the dimension scales of nanometers and micrometers respectively. They are simple machines with limited capabilities and

| System          | Architecture Design     | 25(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

resources that include sensing, simple computations, small memory and data transmission in short distances. Biological sensors, inside the human body and sensors integrated in things, such as books or keys are two example types of nano- and micro- sensing. The rise of these two technologies (and combinational schemes of them) is expected to have great impact in many aspects of social life, such as homeland security or environmental protection.

Such devices are often integrated in larger units to form nano- or micro-machines dedicated to sensing or actuation functionalities. Interconnections of these machines create networks able to serve applications in larger areas, expanding the degree of range and complexity. Further, these networks can communicate with other networks or connect on Internet based applications to make the distribution of information even more widespread.

Nano-engineering is one of the new eras of technological challenge and the research is on going. In this context, the communication techniques of these networks are still immaturely standardized. It is usually not crystal clear how these small devices communicate. Furthermore, a lot depend on the topology, the components and network architecture of the specific application. It is self-evident that the development of nanonetworks implies the arrangement of a wide set of parameters (just like every communication network), including:

- Architectural framework (sensors, routers, gateways) •

- Frequency band of operation

- Channel modelling (path-loss, noise, bandwidth and capacity) •

- Modulation

- Protocols (MAC addressing, routing, service discovery)

Therefore, a brief technical summary of the pSHIELD nano- and micro- platform is considered useful, in contrast to further theoretical definitions.

The pilot demonstrator of pSHIELD uses the Sun SPOT sensor platform as micro node. Sun SPOT is a useful platform for developing and prototyping application for sensor network and embedded system. Sun SPOT is suitable for application areas such as robotics, surveillance and tracking.

#### 3.2.1.1 Technology Description

#### Hardware components

The main units are Sunspot devices with embedded sensors and base station. Each Sunspot has a so-called eSPOT with battery, while the base station is not equipped with battery and must be powered from the host computer via a USB cable. The Sunspot does not need to run any operating system, it needs only JVM that runs on bare metal and executes directly out of flash memory. Stackboards are composed of specific sensors and actuators such as accelerometers. light sensors and temperature sensors. The hardware components of a sensor board are as follows:

- 180MHz for 32-bit ARM920T core processor with 512K RAM and 4M Flash, runs on Squawk

- 2,4GHz based IEEE 802.15.4 radio (radio ChipCon TI CC2420) which is integrated in the • antenna

- USB interface for connecting to a host computer •

- 3.7V battery (720 mAh), Sleep mode (32 uA)

- 3 axis accelerometer (2G/6G) •

- tri-color LEDs, 2 push-buttons control switches

- digital I/O pins, 6 analog inputs, 4 digital outputs

#### Integrated sensors

Temperature Sensor: Chip-type is ADT7411 sensor that measures temperature with ADC. ADC is integrated into eDemo, and can measure temperatures between -40°C to +125°C

| System          | Architecture Design     | 26(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

- Accelerometer sensor: 3-axis accelerometer of the type LIS3L02AQ, designed by ST Micro Systems and located in eDemo Board. This sensor can measure the x-axis, y-axis and z-axis in the direction up and down with the value either ±2G or ±6G. When the Sunspot is at rest, it measures x = y = 0 and z = 1G

- Light sensor is of the type TPS851, designed by Toshiba. The sensor can measure the voltage between 0.1V (dark) 4.3V (light), and converts the voltage to the brightness of Luminance (lx) 3

#### Software components: SUN SPOT JVM

Squawk is open source and has been written in the Java programming language. It is a virtual machine, and is a highly portable Java VM. The advantage of Squawk is that it can run on bare metal instead of being run on top of the operating system. This means that applications can be isolated and be treated as application objects. This allows multiple applications running on the same virtual machine. Squawk also supports CLDC 1.1 that facilitates connectivity to mobile phones.

#### 3.2.2 Power Node

The Power Node is a rugged embedded system, providing high computing power, optimally designed in terms of dimensions, weight, power consumption and capable to work in harsh environmental conditions. The reference application context is defence/aerospace ground mobile and airborne environments, addressing manned and unmanned applications where reliable high performance computing is required.

The Power Node is a pSHIELD SPD Embedded System Device. It is a physical component that offers native SPD features at different abstraction levels: hardware, firmware, network and operating system. The native support of SPD features and the high level of standard adopted, in terms of hardware architecture and operating system, make it ready to host middleware and overlay services.

The node offers low level native SPD capabilities, which are available as hardware components, hardware interfaces, firmware functionalities and network functionalities.

Figure 9 – Power Node pSHIELD component

The node hardware capabilities are focused on security, dependability and composability. These features are provided by the architecture of the node, by the hardware components available on it, by

| System          | Architecture Design     | 27(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

its hardware interfaces, by the firmware and by the compliance with MIL standards. The features include:

- components which can be reconfigured (i.e. FPGA) and interfaces that allows reconfiguration at system level (redundant power supply, node redundancy, spare node, etc.)

- set of FPGA SPD core blocks

- firmware that supports remote reconfiguration of BIOS, FPGA images, etc.

- power supply monitoring and protection unit

- monitoring devices that allow to control continuously the status of the node

- programmable I/O and network interface

- BMC embedded unit

- MIL standard to ensure that the node is capable to work in critical environmental conditions

The node hardware functionalities intend to support security, privacy and dependability. These functionalities are based on the capabilities and features offered by the hardware available on the Power Node board. The functionalities include:

- reconfigurablity functionalities for components, interfaces and firmware

- functionalities for security monitoring (through a dedicated FPGA core logic)

- cryptographic functionalities (through a dedicated core of the FPGA or using Intel AES-NI technology)

- functionalities to monitor continuously working parameters, performance and status of node

- composability functionalities that allow to implement networks of Power Nodes, increasing fault tolerance, computing power, security and dependability

The network services are oriented to increase privacy and dependability. These services are intended mainly to provide some Power Node hardware functionalities remotely. The network services include:

- services for remote reconfiguration of BIOS and FPGA

- SNMP services

- · services for remote self-test and performance monitoring

- privacy and login management services

The node SPD services rely on the hardware capabilities and functionalities, on the network services and on the operating system, offering a set of more abstract services that can be used by the middleware and overlay layers. The set of services includes:

- FPGA and BIOS reconfiguration services

- privacy and user control services

- composability services

- status and performance monitoring services;

- services for the management of the topology of Power Nodes Network

The Power Node has been conceived to host entire parts of the pSHIELD middleware and of the pSHIELD overlay, in particular when the requirements in terms of computing power, hardware composability and reliability are important. In this context, it acts as a computing and reasoning node, more than a data acquisition node. The middleware and overlay services that can be hosted depend on the application context and the role of the parts themselves. From an operating system and application point of view the Power Node can be seen as a very powerful rugged personal computer therefore, any part of the pSHIELD middleware and overlay that runs on a PC may run also on the Power Node.

| System          | Architecture Design     | 28(112)    |

|-----------------|-------------------------|------------|

| Document No.    | Security Classification | Date       |

| /pSHIELD/D2.3.2 | PU                      | 09.12.2011 |

#### 3.2.3 Cryptography Technologies

This section presents in a summarized way the most relevant cryptography technologies related terms and definitions used in pSHIELD project. It is divided in the following sections: attacks on cryptosystems, attacks on protocols, asymmetric and symmetric cryptography, message authentication codes and key management.

#### 3.2.3.1 Attacks on Cryptosystems

There are a number of techniques that have been used in the past to exploit weaknesses of some cryptographic algorithms and are currently used as basic evaluation criteria for new algorithms. The common aim of these attacks is to reveal partially or entirely the information encrypted in intercepted messages, or to extract some information internal to the encryption process (without initially knowing any secrets). They include:

- Brute force attack traversing the entire encryption key space in order to learn the encryption key

- Dictionary attack related to the brute force attack in that a set of keywords are used as possible values of the encryption key (or a pass phrase)

- Chosen cipher text attack obtaining information about a secret decryption key by submitting a range of cipher texts to decrypt

- Adaptive chosen cipher text attack a version of chosen cipher text attack in which the attacker interactively selects subsequent cipher texts based on the results of decryption of the previous ones

- Cipher text-only attack the attacker has access to a limited set of cipher texts

- Known plain text attack the attacker has access to a number of cipher texts together with the corresponding plain texts

- Chosen plain text attack the attacker can encrypt an arbitrary set of chosen plain texts

- Adaptive chosen plain text attack like above, but the attacker chooses subsequent plain text for encryption based on the previous results

- Related-key attack the attacker has access to encryption of a plain text under several different keys whose exact values may not be known but which are somehow mathematically related